Circuitos Sequenciais para banca de Aviônicos

Introdução aos Circuitos Sequenciais

Os circuitos sequenciais representam uma categoria fundamental de circuitos digitais que se distinguem dos circuitos combinacionais por uma característica essencial: suas saídas dependem não apenas das entradas atuais, mas também dos estados anteriores que foram armazenados no sistema.

Esta propriedade de “memória” torna os circuitos sequenciais elementos indispensáveis na construção de sistemas digitais complexos, desde simples contadores até processadores modernos.

Definição e Características Fundamentais

Um circuito sequencial pode ser formalmente definido como um sistema digital cujas saídas em um determinado instante dependem das entradas aplicadas naquele momento e também do histórico de entradas anteriores.

Esta dependência temporal é implementada através de elementos de memória que armazenam informações sobre estados passados do sistema.

A principal diferença entre circuitos combinacionais e sequenciais reside exatamente nesta capacidade de armazenamento. Enquanto um circuito combinacional produz uma saída que é função exclusiva das entradas presentes, um circuito sequencial mantém um “estado interno” que influencia o comportamento futuro do sistema.

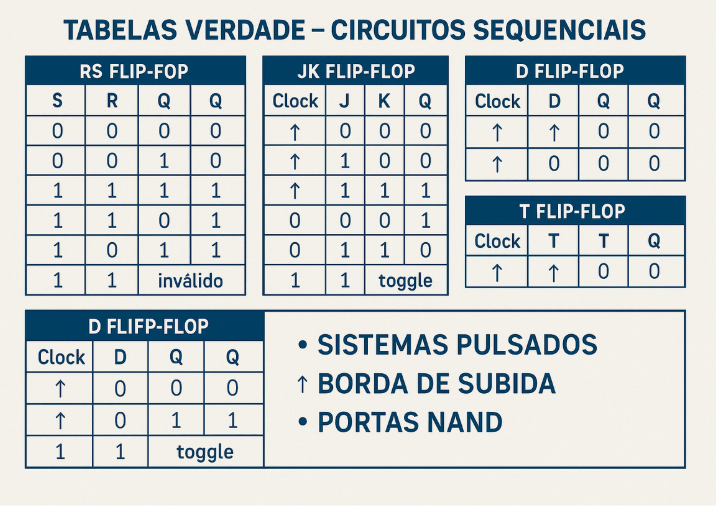

Sistemas Pulsados e o Conceito de Clock

Ponto importante para a banca ANAC: Os circuitos sequenciais são normalmente sistemas pulsados que operam sob o comando de pulsos denominados “clock”. Este conceito é fundamental para compreender o funcionamento de todos os tipos de flip-flops que serão estudados.

O sinal de clock é um sinal periódico que sincroniza as operações do circuito sequencial. Ele determina os instantes precisos em que as mudanças de estado podem ocorrer, garantindo que o sistema opere de forma ordenada e previsível. Sem esta sincronização, os circuitos sequenciais seriam propensos a condições de corrida (race conditions) e comportamentos indeterminados.

O clock apresenta duas transições importantes:

- Borda de subida (↑): Transição do nível lógico baixo (0) para o nível lógico alto (1)

- Borda de descida (↓): Transição do nível lógico alto (1) para o nível lógico baixo (0)

A maioria dos flip-flops utilizados em sistemas digitais modernos são sensíveis à borda de subida do clock, significando que as mudanças de estado ocorrem exclusivamente durante esta transição específica.

Elementos de Memória: Flip-Flops

Os flip-flops constituem os blocos construtivos fundamentais dos circuitos sequenciais. Estes dispositivos são capazes de armazenar um bit de informação e mantê-lo estável até que uma nova informação seja escrita. Cada flip-flop possui dois estados estáveis, representando os valores lógicos 0 e 1.

A capacidade de um flip-flop de manter seu estado indefinidamente (desde que a alimentação seja mantida) é o que permite a construção de sistemas de memória e a implementação de lógica sequencial complexa. Esta estabilidade é alcançada através de realimentação positiva em configurações específicas de portas lógicas.

Aplicações dos Circuitos Sequenciais

Os circuitos sequenciais encontram aplicação em praticamente todos os sistemas digitais modernos:

Contadores: Utilizados para contar eventos, gerar sequências numéricas e implementar divisores de frequência. São essenciais em relógios digitais, temporizadores e sistemas de controle.

Registradores: Armazenam temporariamente dados em processadores e sistemas de comunicação. Permitem o armazenamento paralelo de múltiplos bits de informação.

Memórias: Desde simples latches até complexas memórias RAM, todos os sistemas de armazenamento digital baseiam-se em princípios de circuitos sequenciais.

Máquinas de Estado: Implementam controle sequencial em sistemas complexos, permitindo que dispositivos respondam de forma diferente às mesmas entradas, dependendo de seu estado atual.

Classificação dos Circuitos Sequenciais

Os circuitos sequenciais podem ser classificados de acordo com diferentes critérios:

Quanto à sincronização:

- Síncronos: Operam sob controle de um sinal de clock comum

- Assíncronos: Respondem imediatamente às mudanças nas entradas

Quanto ao tipo de resposta:

- Sensíveis ao nível: Respondem ao nível lógico do sinal de controle

- Sensíveis à borda: Respondem apenas às transições do sinal de controle

Para a banca ANAC, o foco principal está nos circuitos sequenciais síncronos sensíveis à borda de subida, que representam a tecnologia predominante em sistemas digitais modernos.

Flip-Flop RS (Reset-Set)

O Flip-Flop RS, também conhecido como Flip-Flop Set-Reset, representa o tipo mais fundamental de elemento de memória digital. Este dispositivo possui a capacidade de armazenar um bit de informação e é considerado a base para compreender todos os outros tipos de flip-flops utilizados em sistemas digitais.

Características Fundamentais

Ponto importante para a banca ANAC: O Flip-Flop é um dispositivo que possui dois estados estáveis. Um pulso em suas entradas poderá ser armazenado e transformado em nível lógico estável.

O Flip-Flop RS possui duas entradas de controle e duas saídas complementares:

Entradas:

- S (Set): Entrada de ajuste ou configuração

- R (Reset): Entrada de reset ou limpeza

Saídas:

- Q: Saída principal

- Q̅ (Q barra): Saída complementar (sempre oposta a Q)

Funcionamento Básico do RS Latch

O comportamento do Flip-Flop RS pode ser descrito da seguinte forma:

Operação SET: Um pulso na entrada “S” será armazenado, tornando “Q” verdadeiro (Q = 1) e “Q̅” falso (Q̅ = 0). Esta operação “ajusta” ou “configura” o flip-flop para o estado lógico alto.

Operação RESET: Um pulso na entrada “R” será armazenado, tornando “Q” falso (Q = 0) e “Q̅” verdadeiro (Q̅ = 1). Esta operação “reseta” ou “limpa” o flip-flop para o estado lógico baixo.

Convenções de notação:

- Q verdadeiro = Q = 1

- Q falso = Q = 0

Implementação com Portas NAND

Ponto específico da banca ANAC: Um flip-flop tipo RS emprega duas portas NAND em sua implementação básica.

A implementação mais comum do Flip-Flop RS utiliza duas portas NAND conectadas em configuração de realimentação cruzada. Esta configuração cria um circuito biestável onde cada porta NAND controla o estado da outra, resultando em dois estados estáveis possíveis.

A escolha das portas NAND para esta implementação deve-se às suas características lógicas que permitem a criação de um sistema de realimentação positiva estável. Quando uma das saídas está em nível alto, ela mantém a outra saída em nível baixo através da realimentação, criando assim a estabilidade necessária para o armazenamento de informação.

Tabela Verdade do Flip-Flop RS Latch

Ponto importante para a banca ANAC: A tabela verdade mostra quando ocorre alteração na saída.

| S | R | Q | Q̅ | Descrição |

|---|---|---|---|---|

| 0 | 0 | Qprev | Q̅prev | Sem alteração (estado anterior é mantido) |

| 0 | 1 | 0 | 1 | Reset (Q = 0) |

| 1 | 0 | 1 | 0 | Set (Q = 1) |

| 1 | 1 | X | X | Condição inválida (indeterminação, não permitido) |

Análise Detalhada dos Estados

Estado de Memória (S = 0, R = 0): Quando ambas as entradas estão em nível baixo, o flip-flop mantém seu estado anterior. Esta é a condição normal de operação quando não há comando para mudança de estado. O valor armazenado permanece inalterado indefinidamente.

Estado de Reset (S = 0, R = 1): A ativação da entrada R força a saída Q para o nível lógico baixo (0) e a saída Q̅ para o nível lógico alto (1). Esta operação é independente do estado anterior do flip-flop.

Estado de Set (S = 1, R = 0): A ativação da entrada S força a saída Q para o nível lógico alto (1) e a saída Q̅ para o nível lógico baixo (0). Novamente, esta operação é independente do estado anterior.

Estado Inválido (S = 1, R = 1): Esta condição deve ser evitada pois resulta em comportamento indeterminado. Quando ambas as entradas são ativadas simultaneamente, ambas as saídas tendem a ir para o mesmo nível lógico, violando a propriedade fundamental de que Q e Q̅ devem ser sempre complementares. Além disso, quando esta condição é removida, o estado final do flip-flop torna-se imprevisível.

Limitações do RS Latch Básico

O Flip-Flop RS básico (latch) apresenta algumas limitações importantes:

Sensibilidade contínua às entradas: O latch responde imediatamente a qualquer mudança nas entradas S e R, o que pode causar problemas em sistemas síncronos onde é necessário controlar precisamente quando as mudanças de estado ocorrem.

Condição de estado inválido: A possibilidade de aplicar S = R = 1 representa uma limitação significativa que deve ser cuidadosamente evitada no projeto de sistemas digitais.

Problemas de temporização: Em sistemas complexos, diferentes atrasos de propagação podem causar condições de corrida indesejáveis.

Estas limitações levaram ao desenvolvimento do Flip-Flop RS com controle de clock, que será abordado na próxima seção.

Flip-Flop RS com Clock

A evolução natural do Flip-Flop RS básico resultou no desenvolvimento da versão com controle de clock, que resolve muitas das limitações do latch simples e proporciona controle temporal preciso sobre as operações de mudança de estado.

Conceito de Sincronização por Clock

Ponto fundamental para a banca ANAC: Somente ocorre alteração na saída quando o clock sobe (borda de subida).

O Flip-Flop RS com clock incorpora uma entrada adicional de controle temporal denominada CLK (Clock). Esta entrada determina exatamente quando as mudanças de estado podem ocorrer, proporcionando sincronização precisa em sistemas digitais complexos.

A principal vantagem desta abordagem é que as entradas S e R podem mudar a qualquer momento, mas suas alterações só serão efetivadas nas saídas durante a transição específica do sinal de clock. Isto elimina problemas de temporização e permite a construção de sistemas síncronos confiáveis.

Funcionamento Sincronizado

O comportamento do Flip-Flop RS com clock pode ser descrito através dos seguintes princípios:

Sensibilidade à borda de subida: O flip-flop responde às entradas S e R apenas durante a transição do clock de nível baixo para nível alto (↑). Fora deste momento específico, mudanças nas entradas S e R são ignoradas.

Estabilidade entre bordas: Entre as bordas ativas do clock, o flip-flop mantém seu estado atual, independentemente de qualquer atividade nas entradas S e R.

Sincronização de sistema: Todos os flip-flops em um sistema digital podem compartilhar o mesmo sinal de clock, garantindo que todas as mudanças de estado ocorram simultaneamente e de forma coordenada.

Tabela Verdade do Flip-Flop RS com Clock

Ponto específico da banca ANAC: A tabela verdade mostra como a saída do FF responde a uma borda de subida na entrada CLK, para várias combinações das entradas S e R.

| Clock (↑) | S | R | Q (saída) | Q̅ (saída complementar) | Descrição |

|---|---|---|---|---|---|

| ↑ | 0 | 0 | Qprev | Q̅prev | Mantém estado anterior |

| ↑ | 0 | 1 | 0 | 1 | Reset (força saída para 0) |

| ↑ | 1 | 0 | 1 | 0 | Set (força saída para 1) |

| ↑ | 1 | 1 | X | X | Condição inválida (estado proibido) |

Análise Detalhada das Operações Sincronizadas

Operação de Memória Sincronizada (S = 0, R = 0): Quando ambas as entradas de controle estão inativas durante uma borda de subida do clock, o flip-flop preserva seu estado anterior. Esta é a operação mais comum, permitindo que o dispositivo funcione como elemento de memória estável.

Operação de Set Sincronizada (S = 1, R = 0): Durante uma borda de subida do clock, se S = 1 e R = 0, a saída Q é forçada para o nível lógico alto (1) e Q̅ para o nível lógico baixo (0). Esta operação ocorre independentemente do estado anterior do flip-flop.

Operação de Reset Sincronizada (S = 0, R = 1): Durante uma borda de subida do clock, se S = 0 e R = 1, a saída Q é forçada para o nível lógico baixo (0) e Q̅ para o nível lógico alto (1).

Condição Inválida Persistente (S = 1, R = 1): Mesmo com controle de clock, a condição S = R = 1 continua sendo inválida e deve ser evitada. O comportamento resultante permanece indeterminado e pode causar instabilidade no sistema.

Vantagens do Controle por Clock

A incorporação do controle de clock proporciona várias vantagens significativas:

Eliminação de condições de corrida: Como todas as mudanças ocorrem em momentos bem definidos, problemas de temporização entre diferentes partes do sistema são minimizados.

Facilidade de projeto: Sistemas síncronos são mais fáceis de projetar, analisar e depurar comparados a sistemas assíncronos.

Previsibilidade temporal: O comportamento do sistema torna-se completamente previsível em relação ao tempo, facilitando a análise de temporização.

Compatibilidade sistêmica: Múltiplos flip-flops podem operar de forma coordenada usando o mesmo sinal de clock.

Implementação Prática

Na prática, o Flip-Flop RS com clock é implementado adicionando portas lógicas de controle ao circuito básico do latch RS. Estas portas adicionais, tipicamente portas AND, são conectadas entre as entradas S e R originais e o circuito latch interno.

O sinal de clock é aplicado a estas portas de controle, permitindo que os sinais S e R alcancem o latch interno apenas quando o clock está no estado ativo (durante a borda de subida). Quando o clock está inativo, as portas de controle bloqueiam efetivamente qualquer mudança, mantendo o estado do latch inalterado.

Considerações de Temporização

Para operação correta, os sinais S e R devem satisfazer certos requisitos de temporização em relação ao clock:

Tempo de setup: S e R devem estar estáveis por um período mínimo antes da borda ativa do clock.

Tempo de hold: S e R devem permanecer estáveis por um período mínimo após a borda ativa do clock.

Estes requisitos garantem que o flip-flop capture corretamente os valores das entradas durante a transição do clock, evitando estados metaestáveis ou capturas incorretas de dados.

Flip-Flop JK (Jack Kilby)

O Flip-Flop JK representa uma evolução significativa do Flip-Flop RS, eliminando a condição de estado inválido e introduzindo uma funcionalidade adicional extremamente útil: o modo de comutação (toggle mode). Este tipo de flip-flop recebeu seu nome em homenagem a Jack Kilby, um dos pioneiros da eletrônica digital.

Características Fundamentais

Ponto importante para a banca ANAC: O flip-flop J-K é disparado por borda de subida do sinal de clock e possui as entradas J e K que controlam o estado lógico do FF.

O Flip-Flop JK mantém a estrutura básica de um flip-flop com clock, mas substitui as entradas S e R por entradas J e K, respectivamente. Esta mudança não é apenas cosmética, mas representa uma melhoria funcional fundamental que elimina o estado inválido presente no Flip-Flop RS.

Entradas:

- J: Entrada equivalente ao Set (S) do flip-flop RS

- K: Entrada equivalente ao Reset (R) do flip-flop RS

- CLK: Entrada de clock para sincronização

Saídas:

- Q: Saída principal

- Q̅: Saída complementar

Implementação com Portas NAND

Ponto específico da banca ANAC: O flip-flop JK utiliza 4 portas NAND em sua implementação.

A implementação do Flip-Flop JK requer uma configuração mais complexa que o RS básico, utilizando quatro portas NAND interconectadas de forma específica. Esta configuração adicional é necessária para implementar a funcionalidade de toggle e eliminar o estado inválido.

A arquitetura com quatro portas NAND permite que o flip-flop JK implemente realimentação das saídas para as entradas, criando a capacidade de comutação automática quando J = K = 1. Esta realimentação é a chave para o funcionamento do modo toggle, diferenciando fundamentalmente o JK do RS.

Modo de Comutação (Toggle Mode)

Ponto crucial para a banca ANAC: O modo de comutação (toggle mode) ocorre quando J = K = 1, fazendo com que o FF mude para o estado lógico oposto no instante da borda de subida do sinal de clock.

O modo toggle representa a principal inovação do Flip-Flop JK. Quando ambas as entradas J e K são mantidas em nível lógico alto (1) e ocorre uma borda de subida do clock, o flip-flop automaticamente inverte seu estado atual:

- Se Q estava em 0, passa para 1

- Se Q estava em 1, passa para 0

Esta funcionalidade é extremamente útil na construção de contadores binários e divisores de frequência, onde é necessário alternar estados de forma regular e controlada.

Tabela Verdade do Flip-Flop JK

| Clock (↑) | J | K | Q (saída) | Q̅ (saída complementar) | Descrição |

|---|---|---|---|---|---|

| ↑ | 0 | 0 | Qprev | Q̅prev | Mantém estado anterior (Memória) |

| ↑ | 0 | 1 | 0 | 1 | Reset (força saída para 0) |

| ↑ | 1 | 0 | 1 | 0 | Set (força saída para 1) |

| ↑ | 1 | 1 | Q̅prev | Qprev | Toggle (comutação) – saída inverte o valor anterior |

Análise Detalhada dos Estados

Estado de Memória (J = 0, K = 0): Quando ambas as entradas estão em nível baixo durante uma borda de subida do clock, o flip-flop preserva seu estado anterior. Este comportamento é idêntico ao do Flip-Flop RS e permite que o dispositivo funcione como elemento de memória estável.

Estado de Reset (J = 0, K = 1): Esta combinação força a saída Q para 0 durante a próxima borda de subida do clock, independentemente do estado anterior. O comportamento é equivalente à operação de reset do Flip-Flop RS.

Estado de Set (J = 1, K = 0): Esta combinação força a saída Q para 1 durante a próxima borda de subida do clock, independentemente do estado anterior. O comportamento é equivalente à operação de set do Flip-Flop RS.

Estado de Toggle (J = 1, K = 1): Esta é a condição que diferencia fundamentalmente o JK do RS. Em vez de resultar em um estado inválido, esta combinação causa a inversão do estado atual do flip-flop. Se Q = 0, torna-se Q = 1; se Q = 1, torna-se Q = 0.

Vantagens do Flip-Flop JK sobre o RS

Eliminação do estado inválido: A principal vantagem do JK é a transformação da condição problemática S = R = 1 em uma funcionalidade útil (toggle mode).

Funcionalidade adicional: O modo toggle proporciona capacidades que não existem no Flip-Flop RS, tornando o JK mais versátil para aplicações específicas.

Maior confiabilidade: A ausência de estados inválidos torna o projeto de sistemas mais robusto e menos propenso a erros.

Compatibilidade: O JK pode substituir um RS em qualquer aplicação, oferecendo funcionalidade adicional sem perda de compatibilidade.

Aplicações Práticas do Modo Toggle

O modo toggle do Flip-Flop JK encontra aplicação em diversas situações práticas:

Contadores binários: Conectando flip-flops JK em cascata com J = K = 1, é possível construir contadores binários eficientes. Cada flip-flop divide a frequência do sinal de entrada por 2.

Divisores de frequência: Um único flip-flop JK em modo toggle atua como divisor de frequência por 2, produzindo um sinal de saída com metade da frequência do clock de entrada.

Geradores de forma de onda: O modo toggle pode ser usado para gerar ondas quadradas com duty cycle de 50% a partir de sinais de clock.

Máquinas de estado: Em sistemas de controle sequencial, o modo toggle permite implementar transições de estado específicas de forma elegante.

Considerações de Projeto

Ao utilizar Flip-Flops JK em projetos, algumas considerações importantes devem ser observadas:

Temporização: Como todos os flip-flops síncronos, o JK requer que as entradas J e K satisfaçam os requisitos de setup e hold time em relação ao clock.

Realimentação: Em aplicações que utilizam realimentação das saídas, é importante considerar os atrasos de propagação para evitar condições de corrida.

Consumo de energia: A implementação com quatro portas NAND resulta em maior consumo de energia comparado ao RS básico, mas este custo é geralmente justificado pela funcionalidade adicional.

Velocidade de operação: A complexidade adicional pode resultar em tempos de propagação ligeiramente maiores, o que deve ser considerado em aplicações de alta velocidade.

Flip-Flop D (Data)

O Flip-Flop D, também conhecido como Flip-Flop de Dados ou Delay Flip-Flop, representa uma simplificação elegante do conceito de flip-flop, eliminando a complexidade de múltiplas entradas de controle e fornecendo uma interface direta e intuitiva para armazenamento de dados digitais.

Características Fundamentais

Ponto importante para a banca ANAC: É disparado na borda de subida do clock e possui apenas uma entrada de controle síncrona, a entrada D, que representa a palavra data (dado).

O Flip-Flop D simplifica drasticamente a interface de controle ao utilizar apenas uma entrada de dados. Esta simplificação elimina completamente a possibilidade de estados inválidos e torna o comportamento do dispositivo completamente determinístico e previsível.

Entradas:

- D (Data): Entrada única de dados

- CLK: Entrada de clock para sincronização

Saídas:

- Q: Saída principal

- Q̅: Saída complementar

Funcionamento Determinístico

Ponto crucial para a banca ANAC: Quando ocorre uma borda de subida do clock, a saída Q assume o mesmo valor lógico presente na entrada D. A saída poderá ser alterada quando o clock sobe – a saída fica igual à entrada. Se for zero na entrada será zero na saída.

O comportamento do Flip-Flop D é extremamente simples e direto:

- Durante cada borda de subida do clock, o valor presente na entrada D é copiado diretamente para a saída Q

- A saída Q̅ sempre apresenta o valor complementar de Q

- Entre as bordas de clock, as saídas permanecem estáveis, independentemente de mudanças na entrada D

Esta simplicidade operacional torna o Flip-Flop D ideal para aplicações onde é necessário armazenar e transferir dados de forma síncrona e confiável.

Tabela Verdade do Flip-Flop D

| Clock (↑) | D | Q (saída) | Q̅ (saída complementar) | Descrição |

|---|---|---|---|---|

| ↑ | 0 | 0 | 1 | Saída zera (Q = 0) |

| ↑ | 1 | 1 | 0 | Saída armazenada como 1 |

Análise do Comportamento

Transferência direta de dados: A principal característica do Flip-Flop D é a transferência direta e transparente do valor da entrada D para a saída Q durante cada borda ativa do clock. Esta operação é completamente determinística – não há ambiguidade sobre qual será o próximo estado.

Ausência de estados inválidos: Diferentemente dos flip-flops RS e JK, o Flip-Flop D não possui combinações de entrada que resultem em estados inválidos ou indeterminados. Qualquer valor aplicado à entrada D resultará em um comportamento bem definido.

Sincronização perfeita: O Flip-Flop D proporciona sincronização perfeita entre entrada e saída, com a saída sempre refletindo o valor da entrada no momento da última borda ativa do clock.

Implementação e Derivação

O Flip-Flop D pode ser implementado de várias formas:

Derivação do JK: Uma implementação comum utiliza um Flip-Flop JK com a entrada D conectada diretamente à entrada J e através de um inversor à entrada K. Desta forma:

- Quando D = 0: J = 0, K = 1 (operação de reset)

- Quando D = 1: J = 1, K = 0 (operação de set)

Implementação direta: Circuitos integrados modernos implementam o Flip-Flop D diretamente usando configurações otimizadas de transistores, resultando em melhor desempenho e menor consumo de energia.

Aplicações Práticas

O Flip-Flop D encontra aplicação em uma ampla variedade de sistemas digitais:

Registradores de dados: Múltiplos flip-flops D podem ser agrupados para formar registradores capazes de armazenar palavras de dados de múltiplos bits. Cada flip-flop armazena um bit da palavra.

Memórias de acesso aleatório: As células básicas de muitas memórias RAM utilizam princípios similares ao Flip-Flop D para armazenamento de dados.

Sincronização de sinais: O Flip-Flop D é frequentemente usado para sincronizar sinais assíncronos com um clock de sistema, eliminando problemas de metaestabilidade.

Atraso de sinais: Como o nome alternativo “Delay Flip-Flop” sugere, este dispositivo pode ser usado para introduzir atrasos controlados em sinais digitais, com o atraso sendo exatamente um período de clock.

Divisão de dados: Em sistemas de comunicação, flip-flops D são usados para capturar e armazenar bits de dados em momentos específicos determinados pelo clock.

Vantagens do Flip-Flop D

Simplicidade de uso: A interface de entrada única torna o Flip-Flop D extremamente fácil de usar e compreender, reduzindo a possibilidade de erros de projeto.

Comportamento determinístico: A ausência de estados inválidos garante comportamento previsível em todas as condições de operação.

Eficiência de área: Em implementações integradas, o Flip-Flop D geralmente requer menos transistores que flip-flops mais complexos.

Velocidade de operação: A simplicidade da lógica interna frequentemente resulta em tempos de propagação menores.

Facilidade de teste: O comportamento simples facilita a verificação e teste de sistemas que utilizam flip-flops D.

Considerações de Temporização

Como todos os flip-flops síncronos, o Flip-Flop D requer atenção cuidadosa aos requisitos de temporização:

Setup time: A entrada D deve estar estável por um período mínimo antes da borda ativa do clock para garantir captura correta dos dados.

Hold time: A entrada D deve permanecer estável por um período mínimo após a borda ativa do clock.

Propagation delay: Existe um atraso entre a borda do clock e a mudança correspondente na saída Q.

Clock-to-output delay: O tempo necessário para que mudanças no clock se reflitam nas saídas.

Metaestabilidade e Sincronização

Um aspecto importante do Flip-Flop D é seu comportamento quando a entrada D muda muito próximo à borda do clock. Nesta situação, o flip-flop pode entrar em um estado metaestável, onde a saída permanece em um nível intermediário por um período indeterminado.

Para minimizar problemas de metaestabilidade:

- Garantir que sinais de entrada satisfaçam os requisitos de setup e hold

- Usar múltiplos estágios de sincronização para sinais assíncronos

- Projetar sistemas com margens adequadas de temporização

Variações do Flip-Flop D

Existem várias variações do Flip-Flop D básico:

D Flip-Flop com preset e clear: Inclui entradas assíncronas para forçar estados específicos independentemente do clock.

D Latch: Versão sensível ao nível em vez de borda, onde a saída segue a entrada quando o enable está ativo.

D Flip-Flop com enable: Inclui uma entrada de habilitação que controla quando o flip-flop responde ao clock.

Flip-Flop T (Toggle)

O Flip-Flop T (Toggle) representa uma especialização do conceito de flip-flop, otimizada especificamente para operações de comutação. Este dispositivo é essencialmente uma versão simplificada do Flip-Flop JK, configurada permanentemente no modo toggle, oferecendo uma interface ainda mais simples para aplicações que requerem alternância de estados.

Características Fundamentais

Ponto importante para a banca ANAC: As saídas Q e Q̅ assumem valor “1” se anteriormente estavam em “0”, e assumem “0” se anteriormente estavam em “1”, mas somente quando a entrada “T” é levada ao nível lógico ALTO (HIGH). É justamente essa ação de comutação assíncrona (toggling) que caracteriza o funcionamento de interesse deste dispositivo.

O Flip-Flop T simplifica ainda mais a interface de controle, utilizando apenas uma entrada de controle que determina se a comutação deve ou não ocorrer:

Entradas:

- T (Toggle): Entrada de controle de comutação

- CLK: Entrada de clock para sincronização

Saídas:

- Q: Saída principal

- Q̅: Saída complementar

Funcionamento da Comutação

O comportamento do Flip-Flop T é caracterizado pela sua capacidade de alternar entre estados de forma controlada:

Modo de preservação (T = 0): Quando a entrada T está em nível baixo durante uma borda de subida do clock, o flip-flop mantém seu estado atual. Não ocorre comutação.

Modo de comutação (T = 1): Quando a entrada T está em nível alto durante uma borda de subida do clock, o flip-flop inverte seu estado atual. Se Q = 0, torna-se Q = 1; se Q = 1, torna-se Q = 0.

Tabela Verdade do Flip-Flop T

| Clock (↑) | T | Q (saída) | Descrição |

|---|---|---|---|

| ↑ | 0 | Qprev | Mantém estado anterior |

| ↑ | 1 | Q̅prev | Toggle (inverte a saída) |

Divisão de Frequência

Ponto específico da banca ANAC: 4 ciclos de clock para 2 ciclos de Q.

Uma das aplicações mais importantes do Flip-Flop T é como divisor de frequência. Quando a entrada T é mantida permanentemente em nível alto (T = 1), o flip-flop atua como um divisor de frequência por 2:

Relação de frequências:

- Frequência de entrada (clock): f_clk

- Frequência de saída (Q): f_clk ÷ 2

Análise temporal:

- Para cada 4 bordas de subida do clock, a saída Q completa 2 ciclos completos

- A saída Q permanece em cada estado (0 ou 1) por exatamente 2 períodos do clock

- O duty cycle da saída Q é sempre 50%, independentemente do duty cycle do clock de entrada

Implementação Prática

O Flip-Flop T pode ser implementado de várias formas:

Derivação do JK: A implementação mais comum utiliza um Flip-Flop JK com as entradas J e K conectadas à entrada T:

- J = T

- K = T

- Quando T = 0: J = K = 0 (modo memória)

- Quando T = 1: J = K = 1 (modo toggle)

Derivação do D: Alternativamente, pode ser implementado usando um Flip-Flop D com realimentação:

- A entrada D é conectada à saída Q̅ através de uma porta XOR com a entrada T

- Quando T = 0: D = Q (mantém estado)

- Quando T = 1: D = Q̅ (inverte estado)

Aplicações Práticas

O Flip-Flop T encontra aplicação em diversas situações onde a comutação controlada é necessária:

Contadores binários: Flip-flops T conectados em cascata formam contadores binários eficientes. Cada estágio divide a frequência por 2, criando uma progressão binária natural.

Divisores de frequência: Aplicação direta como divisor de frequência por potências de 2. Uma cadeia de n flip-flops T produz divisão por 2^n.

Geradores de clock: Criação de sinais de clock com frequências específicas a partir de um oscilador de referência.

Máquinas de estado simples: Em sistemas que alternam entre dois estados, o Flip-Flop T oferece uma solução elegante e eficiente.

Detecção de bordas: Pode ser usado em circuitos de detecção de bordas para identificar transições em sinais digitais.

Análise de Contadores com Flip-Flops T

Quando múltiplos flip-flops T são conectados em cascata para formar um contador:

Contador de 2 bits:

- FF0: divide por 2 (LSB)

- FF1: divide por 4 (MSB)

- Sequência de contagem: 00 → 01 → 10 → 11 → 00…

Contador de 3 bits:

- FF0: divide por 2

- FF1: divide por 4

- FF2: divide por 8

- Conta de 0 a 7 em binário

Contador de n bits:

- Conta de 0 a (2^n – 1)

- Período total = 2^n × período do clock

Vantagens do Flip-Flop T

Simplicidade extrema: Interface de controle com apenas uma entrada torna o uso muito simples.

Eficiência em contadores: Ideal para implementação de contadores binários com mínima complexidade de controle.

Divisão de frequência precisa: Proporciona divisão exata por potências de 2 com excelente precisão.

Baixo consumo: A simplicidade da lógica de controle resulta em menor consumo de energia.

Previsibilidade: Comportamento completamente determinístico facilita análise e projeto.

Considerações de Projeto

Inicialização: Contadores baseados em flip-flops T requerem inicialização adequada para garantir sequência de contagem correta.

Propagação de atraso: Em contadores síncronos, todos os flip-flops mudam simultaneamente, mas em contadores assíncronos (ripple), existe propagação de atraso entre estágios.

Velocidade máxima: A frequência máxima de operação é limitada pelos tempos de propagação dos flip-flops individuais.

Glitches: Em contadores assíncronos, podem ocorrer glitches temporários durante transições devido aos diferentes atrasos de propagação.

Comparação com Outros Flip-Flops

Versus JK: O Flip-Flop T é essencialmente um JK simplificado, oferecendo apenas a funcionalidade de toggle. É mais eficiente quando apenas comutação é necessária.

Versus D: Enquanto o D é ideal para armazenamento de dados, o T é otimizado para comutação. Cada um excele em sua aplicação específica.

Versus RS: O T elimina completamente os problemas de estado inválido do RS, oferecendo funcionalidade de comutação que o RS não possui.

Aplicações Avançadas

Síntese de frequências: Combinando múltiplos divisores T, é possível sintetizar frequências complexas a partir de um oscilador de referência.

Modulação de largura de pulso: Flip-flops T podem ser usados em circuitos PWM para controle de potência.

Sistemas de temporização: Em aplicações que requerem eventos periódicos, o Flip-Flop T oferece uma solução robusta e precisa.

Processamento de sinais digitais: Utilizado em filtros digitais e sistemas de amostragem para controle de temporização.

Pontos Específicos da Banca ANAC

Esta seção consolida todos os pontos fundamentais que são especificamente cobrados pela banca ANAC em relação aos circuitos sequenciais. Estes tópicos representam o conhecimento essencial que deve ser dominado para obter sucesso nas avaliações.

1. Conceitos Fundamentais

Definição de Circuitos Sequenciais:

- Circuitos sequenciais são normalmente sistemas pulsados que operam sob o comando de pulsos denominados “clock”

- As saídas dependem das entradas atuais E dos estados anteriores armazenados

- Diferem dos circuitos combinacionais pela capacidade de memória

Importância do Clock:

- Todas as mudanças de estado ocorrem SOMENTE na borda de subida do clock (↑)

- O clock sincroniza todas as operações do sistema

- Garante operação ordenada e previsível

2. Flip-Flop RS (Reset-Set)

Características Básicas:

- Possui duas entradas (S e R) e duas saídas (Q e Q̅)

- É um dispositivo com dois estados estáveis

- Um pulso nas entradas pode ser armazenado e transformado em nível lógico estável

Implementação:

- Ponto ANAC: Um flip-flop tipo RS emprega duas portas NAND

- A configuração de realimentação cruzada cria estabilidade

Tabela Verdade RS Latch:

| S | R | Q | Q̅ | Descrição |

|---|---|---|---|---|

| 0 | 0 | Qprev | Q̅prev | Sem alteração |

| 0 | 1 | 0 | 1 | Reset (Q = 0) |

| 1 | 0 | 1 | 0 | Set (Q = 1) |

| 1 | 1 | X | X | Condição inválida |

Operação com Clock:

- Ponto ANAC: Alteração na saída SOMENTE quando o clock sobe

- Elimina problemas de temporização do latch básico

3. Flip-Flop JK (Jack Kilby)

Características Principais:

- Ponto ANAC: É disparado por borda de subida do sinal de clock

- Possui entradas J e K que controlam o estado lógico

- Elimina a condição inválida do RS

Implementação:

- Ponto ANAC: Utiliza 4 portas NAND

- Configuração mais complexa que o RS para implementar o modo toggle

Modo Toggle:

- Ponto ANAC: Ocorre quando J = K = 1

- Faz o FF mudar para o estado lógico oposto na borda de subida do clock

- Aplicação: 1 e 1 nas entradas + pulso de subida = alteração de saída

Tabela Verdade JK:

| Clock (↑) | J | K | Q (saída) | Descrição |

|---|---|---|---|---|

| ↑ | 0 | 0 | Qprev | Mantém estado anterior |

| ↑ | 0 | 1 | 0 | Reset |

| ↑ | 1 | 0 | 1 | Set |

| ↑ | 1 | 1 | Q̅prev | Toggle (comutação) |

4. Flip-Flop D (Data)

Características Fundamentais:

- Ponto ANAC: É disparado na borda de subida do clock

- Possui apenas uma entrada de controle síncrona (D)

- D representa “data” (dado)

Funcionamento:

- Ponto ANAC: Quando o clock sobe, a saída fica igual à entrada

- Se for zero na entrada, será zero na saída

- Se for um na entrada, será um na saída

- Comportamento completamente determinístico

Tabela Verdade D:

| Clock (↑) | D | Q (saída) | Descrição |

|---|---|---|---|

| ↑ | 0 | 0 | Saída zera |

| ↑ | 1 | 1 | Saída armazena 1 |

5. Flip-Flop T (Toggle)

Características Específicas:

- Especializado em operações de comutação

- Entrada T controla se a comutação ocorre ou não

Divisão de Frequência:

- Ponto ANAC: 4 ciclos de clock para 2 ciclos de Q

- Atua como divisor de frequência por 2

- Saída Q tem metade da frequência do clock

- Duty cycle de 50% na saída

Aplicação em Contadores:

- Fundamental para contadores binários

- Cada flip-flop T divide a frequência por 2

- Cascateamento permite contagem binária

6. Resumo das Implementações com Portas Lógicas

RS: 2 portas NAND JK: 4 portas NANDD: Derivado do JK ou implementação direta T: Derivado do JK com J = K = T

7. Pontos Críticos para Avaliação

Temporização:

- Todas as mudanças ocorrem na borda de subida do clock

- Setup time e hold time devem ser respeitados

- Propagation delay afeta a velocidade máxima

Estados Inválidos:

- RS: S = R = 1 é inválido

- JK: J = K = 1 é válido (toggle)

- D: Não possui estados inválidos

- T: Não possui estados inválidos

Aplicações Principais:

- RS: Memória básica, latches

- JK: Contadores, aplicações gerais

- D: Registradores, armazenamento de dados

- T: Divisores de frequência, contadores

8. Questões Típicas da Banca ANAC

Tipo 1: “Que tipo de porta lógica um flip-flop RS emprega?” Resposta: Duas portas NAND

Tipo 2: “Quantas portas NAND utiliza um flip-flop JK?” Resposta: 4 portas NAND

Tipo 3: “Quando ocorre alteração na saída de um flip-flop com clock?” Resposta: Somente na borda de subida do clock

Tipo 4: “O que acontece em um flip-flop JK quando J = K = 1?” Resposta: Modo toggle – a saída inverte o estado anterior

Tipo 5: “Como se comporta a saída de um flip-flop D?” Resposta: A saída fica igual à entrada quando o clock sobe

Tipo 6: “Qual a relação entre clock e saída em um flip-flop T?” Resposta: 4 ciclos de clock para 2 ciclos de Q (divisão por 2)

9. Dicas para a Prova

Memorize as tabelas verdade de todos os tipos de flip-flop Entenda a diferença entre latch e flip-flop com clock Saiba identificar o número de portas lógicas em cada implementação Compreenda o conceito de borda de subida e sua importância Pratique análise de timing diagrams Domine o conceito de divisão de frequência com flip-flop T

Relevância para a Banca ANAC

Os pontos específicos cobrados pela banca ANAC refletem aspectos práticos e fundamentais dos circuitos sequenciais. A ênfase na implementação com portas lógicas específicas (2 NAND para RS, 4 NAND para JK) demonstra a importância de compreender não apenas o comportamento funcional, mas também a implementação física dos dispositivos.

O foco na sincronização por clock e na borda de subida reflete a realidade dos sistemas digitais modernos, onde a sincronização precisa é essencial para operação confiável. A compreensão do modo toggle do JK e da divisão de frequência do T são fundamentais para aplicações em contadores e sistemas de temporização.

Aplicações Práticas

Os conhecimentos apresentados neste documento têm aplicação direta em diversas áreas da eletrônica digital:

Sistemas de controle: Flip-flops implementam máquinas de estado que controlam sequências de operações em sistemas automatizados.

Processamento de dados: Registradores baseados em flip-flops D armazenam temporariamente dados em processadores e sistemas de comunicação.

Sistemas de temporização: Contadores baseados em flip-flops T e JK geram sinais de temporização precisos para sincronização de sistemas complexos.

Memórias digitais: Princípios de flip-flops são fundamentais para compreender o funcionamento de todos os tipos de memória digital.

Recomendações para Estudo

Para obter sucesso nas avaliações da banca ANAC, recomenda-se:

- Memorização das tabelas verdade de todos os tipos de flip-flop

- Prática com timing diagrams para compreender comportamento temporal

- Compreensão das implementações com portas lógicas específicas

Resolução de exercícios focados nos pontos específicos da banca.

GLOSSÁRIO

A

AssíncronoTipo de circuito sequencial que responde imediatamente às mudanças nas entradas, sem necessidade de sinal de clock. Contrasta com circuitos síncronos. Exemplo: latch RS básico.

Atraso de Propagação (Propagation Delay)Tempo necessário para que uma mudança na entrada de um circuito se reflita na saída. Parâmetro crítico que determina a velocidade máxima de operação de sistemas digitais.

B

BiestávelCaracterística de um circuito que possui dois estados estáveis distintos. Flip-flops são dispositivos biestáveis por natureza, capazes de manter indefinidamente um de dois estados lógicos (0 ou 1).

BitUnidade básica de informação digital, podendo assumir valor 0 ou 1. Cada flip-flop armazena exatamente um bit de informação.

Borda de ClockTransição do sinal de clock entre níveis lógicos. Borda de subida (↑): transição de 0 para 1. Borda de descida (↓): transição de 1 para 0. A maioria dos flip-flops modernos é sensível à borda de subida.

C

Circuito CombinacionalTipo de circuito digital cujas saídas dependem exclusivamente das entradas atuais, sem capacidade de memória. Contrasta com circuitos sequenciais.

Circuito SequencialCircuito digital cujas saídas dependem tanto das entradas atuais quanto dos estados anteriores armazenados. Possui capacidade de memória através de elementos como flip-flops.

Clock (CLK)Sinal periódico que sincroniza as operações de circuitos sequenciais. Determina os instantes precisos em que mudanças de estado podem ocorrer. Ponto ANAC: Circuitos sequenciais são sistemas pulsados que operam sob comando de pulsos denominados “clock”.

Clock-to-Output DelayTempo decorrido entre a borda ativa do clock e a correspondente mudança na saída do flip-flop. Parâmetro importante para análise de temporização.

Comutação (Toggle)Operação que inverte o estado atual de um flip-flop. Se Q = 0, torna-se Q = 1; se Q = 1, torna-se Q = 0. Característica fundamental do modo toggle dos flip-flops JK e T.

Condição de Corrida (Race Condition)Situação indesejável onde o resultado final depende da sequência temporal relativa de eventos. Eliminada em sistemas síncronos através do uso de clock.

ContadorCircuito sequencial que produz uma sequência específica de estados em resposta a pulsos de entrada. Construído tipicamente com flip-flops conectados em cascata.

Contador Assíncrono (Ripple Counter)Contador onde os flip-flops não compartilham o mesmo clock, resultando em propagação sequencial de mudanças. Também conhecido como contador ripple.

Contador SíncronoContador onde todos os flip-flops são controlados pelo mesmo sinal de clock, resultando em mudanças simultâneas de estado.

D

Data (D)Entrada de dados do Flip-Flop D. O valor presente nesta entrada é transferido para a saída Q durante a borda ativa do clock. Ponto ANAC: Representa a palavra “data” (dado).

Delay Flip-FlopNome alternativo para o Flip-Flop D, enfatizando sua capacidade de introduzir atraso controlado (um período de clock) em sinais digitais.

DeterminísticoCaracterística de sistemas cujo comportamento é completamente previsível. O Flip-Flop D é determinístico pois não possui estados inválidos.

Divisor de FrequênciaCircuito que produz sinal de saída com frequência que é uma fração da frequência de entrada. Ponto ANAC: Flip-flop T atua como divisor por 2 (4 ciclos de clock para 2 ciclos de Q).

Duty CyclePercentual do período total em que um sinal permanece em nível alto. Flip-flops T em modo toggle produzem saídas com duty cycle de 50%.

E

EnableSinal de controle que habilita ou desabilita a operação de um circuito. Alguns flip-flops possuem entrada de enable além do clock.

EstadoCondição atual de um sistema sequencial, determinada pelos valores armazenados em seus elementos de memória. Cada flip-flop contribui com um bit para o estado total do sistema.

Estado EstávelCondição onde um circuito permanece inalterado na ausência de mudanças nas entradas. Flip-flops possuem dois estados estáveis (0 e 1).

Estado InválidoCombinação de entradas que resulta em comportamento indeterminado. Ponto ANAC: No flip-flop RS, S = R = 1 é condição inválida.

Estado MetaestávelCondição instável onde a saída de um flip-flop permanece em nível intermediário quando requisitos de temporização não são satisfeitos.

F

Flip-FlopDispositivo digital biestável capaz de armazenar um bit de informação. Ponto ANAC: Possui dois estados estáveis e pode armazenar pulsos transformando-os em níveis lógicos estáveis.

Flip-Flop DTipo de flip-flop com entrada única de dados. Ponto ANAC: Disparado na borda de subida do clock, a saída Q assume o mesmo valor da entrada D.

Flip-Flop JKEvolução do flip-flop RS que elimina o estado inválido. Ponto ANAC: Disparado por borda de subida, utiliza 4 portas NAND, modo toggle quando J = K = 1.

Flip-Flop RSTipo fundamental de flip-flop com entradas Set e Reset. Ponto ANAC: Emprega duas portas NAND, possui condição inválida quando S = R = 1.

Flip-Flop TFlip-flop especializado em comutação. Ponto ANAC: Produz 2 ciclos de saída para cada 4 ciclos de clock, atuando como divisor de frequência.

FrequênciaNúmero de ciclos completos de um sinal periódico por unidade de tempo, medida em Hertz (Hz). Flip-flops T dividem a frequência do clock por 2.

G

GlitchPulso espúrio de curta duração que pode aparecer em saídas de circuitos digitais devido a diferentes atrasos de propagação. Comum em contadores assíncronos.

H

Hold TimeTempo mínimo que as entradas de um flip-flop devem permanecer estáveis após a borda ativa do clock. Requisito crítico para operação correta.

HIGH (Alto)Nível lógico correspondente ao valor binário 1. Ponto ANAC: Flip-flop T comuta quando entrada T é levada ao nível lógico alto.

I

IndeterminadoEstado onde o valor lógico não pode ser previsto com certeza. Ocorre em condições inválidas de flip-flops ou violações de temporização.

InicializaçãoProcesso de estabelecer estados conhecidos em circuitos sequenciais no momento da energização. Essencial para operação previsível de contadores e registradores.

J

J (Jack)Entrada do flip-flop JK equivalente à entrada Set do flip-flop RS. Quando J = 1 e K = 0, o flip-flop é ajustado para Q = 1.

Jack KilbyPioneiro da eletrônica digital que deu nome ao flip-flop JK. Inventor do circuito integrado.

K

K (Kilby)Entrada do flip-flop JK equivalente à entrada Reset do flip-flop RS. Quando J = 0 e K = 1, o flip-flop é resetado para Q = 0.

L

LatchTipo de elemento de memória sensível ao nível do sinal de controle, em contraste com flip-flops que são sensíveis à borda. Ponto ANAC: Flip-flop RS básico é um latch.

LOW (Baixo)Nível lógico correspondente ao valor binário 0. Estado de referência em sistemas digitais.

LSB (Least Significant Bit)Bit menos significativo em uma representação binária. Em contadores, corresponde ao flip-flop que muda de estado com maior frequência.

M

Máquina de EstadoSistema sequencial que pode estar em um número finito de estados e transiciona entre eles baseado em entradas e estado atual. Implementada usando flip-flops.

MemóriaCapacidade de um sistema de reter informação. Característica fundamental que distingue circuitos sequenciais de combinacionais.

MetaestabilidadeFenômeno onde um flip-flop entra em estado instável quando requisitos de temporização não são satisfeitos, podendo resultar em saída indeterminada.

Modo ToggleOperação onde um flip-flop inverte seu estado atual. Ponto ANAC: No JK, ocorre quando J = K = 1; no T, quando T = 1.

MSB (Most Significant Bit)Bit mais significativo em uma representação binária. Em contadores, corresponde ao flip-flop que muda de estado com menor frequência.

N

NANDPorta lógica que produz saída baixa apenas quando todas as entradas são altas. Ponto ANAC: Flip-flop RS usa 2 portas NAND; JK usa 4 portas NAND.

Nível LógicoEstado de um sinal digital, podendo ser alto (1) ou baixo (0). Base da representação de informação em sistemas digitais.

O

OscilaçãoMudança periódica entre estados. Flip-flops em modo toggle produzem oscilação controlada na saída.

P

PeríodoTempo necessário para um sinal periódico completar um ciclo completo. Relacionado inversamente com a frequência.

Porta LógicaCircuito eletrônico que implementa uma função lógica básica (AND, OR, NOT, NAND, etc.). Blocos construtivos fundamentais de flip-flops.

PresetEntrada assíncrona que força um flip-flop para o estado Q = 1, independentemente do clock. Também conhecida como Set assíncrono.

PulsoMudança temporária em um sinal digital, retornando ao estado original após período determinado. Ponto ANAC: Circuitos sequenciais operam sob comando de pulsos de clock.

Q

QSaída principal de um flip-flop. Representa o estado atual armazenado no dispositivo. Convenção ANAC: Q verdadeiro = Q = 1; Q falso = Q = 0.

Q̅ (Q barra)Saída complementar de um flip-flop, sempre oposta à saída Q. Se Q = 1, então Q̅ = 0, e vice-versa.

Qprev (Q anterior)Notação usada em tabelas verdade para indicar que a saída mantém o valor do estado anterior. Representa operação de memória.

R

Race ConditionVer “Condição de Corrida”. Situação problemática eliminada pelo uso de sincronização por clock.

RealimentaçãoConexão da saída de um circuito de volta à sua entrada. Fundamental para criar estabilidade em flip-flops e implementar modo toggle.

RegistradorConjunto de flip-flops usado para armazenar uma palavra de dados de múltiplos bits. Cada flip-flop armazena um bit da palavra.

ResetOperação que força um flip-flop para o estado Q = 0. Ponto ANAC: No RS, ocorre quando S = 0 e R = 1.

Ripple CounterVer “Contador Assíncrono”. Tipo de contador onde mudanças se propagam sequencialmente através dos estágios.

S

S (Set)Entrada do flip-flop RS que, quando ativada, força a saída Q para 1. Ponto ANAC: Um pulso na entrada S torna Q verdadeiro e Q̅ falso.

Sensível à BordaCaracterística de flip-flops que respondem apenas às transições (bordas) do sinal de clock, não ao nível. Contrasta com latches sensíveis ao nível.

Sensível ao NívelCaracterística de latches que respondem ao nível lógico do sinal de controle. Contrasta com flip-flops sensíveis à borda.

SetOperação que força um flip-flop para o estado Q = 1. Oposto de Reset.

Setup TimeTempo mínimo que as entradas de um flip-flop devem estar estáveis antes da borda ativa do clock. Requisito crítico para captura correta de dados.

SíncronoTipo de circuito sequencial onde todas as operações são coordenadas por um sinal de clock comum. Ponto ANAC: Mudanças ocorrem somente na borda de subida do clock.

Sistema PulsadoDefinição ANAC: Circuitos sequenciais são normalmente sistemas pulsados que operam sob comando de pulsos denominados “clock”.

T

T (Toggle)Entrada do flip-flop T que controla se a comutação deve ocorrer. Quando T = 1, o flip-flop inverte seu estado na próxima borda do clock.

Tabela VerdadeRepresentação tabular que mostra todas as combinações possíveis de entradas e suas correspondentes saídas. Ferramenta ANAC: Essencial para compreender comportamento de flip-flops.

TemporizaçãoAspectos relacionados ao tempo em circuitos digitais, incluindo setup time, hold time e propagation delay. Crítico para operação correta de sistemas síncronos.

ToggleVer “Comutação”. Operação de inversão de estado. Ponto ANAC: Característica fundamental dos flip-flops JK (quando J = K = 1) e T (quando T = 1).

TransiçãoMudança de um estado lógico para outro. Bordas de clock são transições específicas que controlam flip-flops.

V

VerdadeiroEstado lógico correspondente ao valor binário 1. Convenção ANAC: Q verdadeiro = Q = 1.

VolatilidadeCaracterística de memórias que perdem informação quando a alimentação é removida. Flip-flops são voláteis.

Siglas e Abreviações Importantes

CLK: Clock (Relógio)D: Data (Dados)FF: Flip-FlopJ: Jack (entrada do flip-flop JK)K: Kilby (entrada do flip-flop JK)LSB: Least Significant Bit (Bit Menos Significativo)MSB: Most Significant Bit (Bit Mais Significativo)Q: Saída principalQ̅: Saída complementar (Q barra)R: ResetS: SetT: Toggle

Fórmulas e Relações Importantes

Divisão de Frequência (Flip-flop T):f_saída = f_clock ÷ 2

Contadores Binários:Número de estados = 2^n (onde n = número de flip-flops)

Período de Contagem:T_contagem = 2^n × T_clock

Aplicações por Tipo de Flip-Flop

RS: Latches básicos, memória simplesJK: Contadores universais, aplicações geraisD: Registradores, armazenamento de dadosT: Divisores de frequência, contadores binários

TABELAS VERDADE COMPLETAS

Tabela Verdade – Flip-Flop RS (Latch)

Descrição: Flip-Flop RS básico sem controle de clock, sensível ao nível das entradas.

| S | R | Q | Q̅ | Descrição |

|---|---|---|---|---|

| 0 | 0 | Qprev | Q̅prev | Sem alteração (estado anterior é mantido) |

| 0 | 1 | 0 | 1 | Reset (Q = 0) |

| 1 | 0 | 1 | 0 | Set (Q = 1) |

| 1 | 1 | X | X | Condição inválida (indeterminação, não permitido) |

Pontos ANAC:

- Alteração na saída se for 1 nas entradas

- Emprega duas portas NAND

- Condição S = R = 1 é inválida

Tabela Verdade – Flip-Flop RS com Clock

Descrição: Flip-Flop RS com controle de clock, mudanças ocorrem apenas na borda de subida.

| Clock (↑) | S | R | Q (saída) | Q̅ (saída complementar) | Descrição |

|---|---|---|---|---|---|

| ↑ | 0 | 0 | Qprev | Q̅prev | Mantém estado anterior |

| ↑ | 0 | 1 | 0 | 1 | Reset (força saída para 0) |

| ↑ | 1 | 0 | 1 | 0 | Set (força saída para 1) |

| ↑ | 1 | 1 | X | X | Condição inválida (estado proibido) |

Pontos ANAC:

- Somente alteração na saída quando o clock sobe

- S = 1, R = 0 → SET: a saída Q é ajustada para 1

- S = 0, R = 1 → RESET: a saída Q é forçada para 0

- S = 0, R = 0 → MEMÓRIA: mantém o estado anterior (Qprev)

- S = 1, R = 1 → INVÁLIDO: gera condição indeterminada

Tabela Verdade – Flip-Flop JK

Descrição: Evolução do RS que elimina o estado inválido, introduzindo o modo toggle.

| Clock (↑) | J | K | Q (saída) | Q̅ (saída complementar) | Descrição |

|---|---|---|---|---|---|

| ↑ | 0 | 0 | Qprev | Q̅prev | Mantém estado anterior (Memória) |

| ↑ | 0 | 1 | 0 | 1 | Reset (força saída para 0) |

| ↑ | 1 | 0 | 1 | 0 | Set (força saída para 1) |

| ↑ | 1 | 1 | Q̅prev | Qprev | Toggle (comutação) – saída inverte o valor anterior |

Pontos ANAC:

- Disparado por borda de subida

- Utiliza 4 portas NAND

- Modo toggle quando J = K = 1

- 1 e 1 nas entradas + pulso de subida = alteração de saída

- Elimina a condição inválida do RS

Diferença em relação ao RS:

- No Flip-Flop RS: S = R = 1 → condição inválida

- No Flip-Flop JK: J = K = 1 → comutação (toggle)

Tabela Verdade – Flip-Flop D

Descrição: Flip-flop determinístico com entrada única de dados.

| Clock (↑) | D | Q (saída) | Q̅ (saída complementar) | Descrição |

|---|---|---|---|---|

| ↑ | 0 | 0 | 1 | Saída zera (Q = 0) |

| ↑ | 1 | 1 | 0 | Saída armazenada como 1 |

Pontos ANAC:

- Disparado na borda de subida do clock

- Entrada D representa “data” (dado)

- A saída fica igual à entrada quando o clock sobe

- Se for zero na entrada será zero na saída

- Não existe estado inválido – é determinístico

- A cada borda de subida do clock, o valor da entrada D é copiado para a saída Q

Tabela Verdade – Flip-Flop T

Descrição: Flip-flop especializado em comutação (toggle).

| Clock (↑) | T | Q (saída) | Descrição |

|---|---|---|---|

| ↑ | 0 | Qprev | Mantém estado anterior |

| ↑ | 1 | Q̅prev | Toggle (inverte a saída) |

Pontos ANAC:

- Comutação quando entrada T é levada ao nível lógico ALTO

- 4 ciclos de clock para 2 ciclos de Q (divisor de frequência por 2)

- Versão simplificada do JK com J = K = 1

- Aplicações: contadores binários e divisores de frequência

- A saída Q oscila com metade da frequência do clock

QUESTÕES TÍPICAS DA BANCA ANAC

Categoria 1: Implementação com Portas Lógicas

Questão: “Um flip-flop tipo RS emprega que tipo de porta lógica?”

Resposta: Duas portas NAND

Questão: “Quantas portas NAND utiliza um flip-flop JK?”

Resposta: 4 portas NAND

Explicação: A implementação do JK é mais complexa que o RS devido à necessidade de implementar o modo toggle e eliminar o estado inválido.

Categoria 2: Sincronização e Clock

Questão: “Quando ocorre alteração na saída de um flip-flop com clock?”

Resposta: Somente na borda de subida do clock

Questão: “O que significa dizer que circuitos sequenciais são sistemas pulsados?”

Resposta: Operam sob o comando de pulsos denominados “clock”

Explicação: A sincronização por clock é fundamental para operação ordenada e eliminação de condições de corrida.

Categoria 3: Flip-Flop JK – Modo Toggle

Questão: “O que acontece em um flip-flop JK quando J = K = 1?”

Resposta: Modo toggle – a saída inverte o estado anterior

Questão: “Como o flip-flop JK é disparado?”

Resposta: Por borda de subida do sinal de clock

Questão: “O que ocorre quando aplico 1 e 1 nas entradas JK e um pulso de subida?”

Resposta: Alteração de saída (comutação/toggle)

Categoria 4: Flip-Flop D – Comportamento

Questão: “Como se comporta a saída de um flip-flop D?”

Resposta: A saída fica igual à entrada quando o clock sobe

Questão: “Se a entrada D for zero, qual será a saída?”

Resposta: Zero na saída

Questão: “O que representa a entrada D?”

Resposta: Data (dado)

Categoria 5: Flip-Flop T – Divisão de Frequência

Questão: “Qual a relação entre clock e saída em um flip-flop T?”

Resposta: 4 ciclos de clock para 2 ciclos de Q

Questão: “Como funciona um flip-flop T como divisor de frequência?”

Resposta: Divide a frequência por 2 – a saída tem metade da frequência do clock

Questão: “Quando ocorre comutação no flip-flop T?”

Resposta: Quando a entrada T é levada ao nível lógico ALTO

Categoria 6: Estados e Condições

Questão: “Qual é a condição inválida do flip-flop RS?”

Resposta: S = R = 1 (gera indeterminação)

Questão: “O flip-flop JK possui estado inválido?”

Resposta: Não, elimina o estado inválido do RS transformando-o em modo toggle

Questão: “Quantos estados estáveis possui um flip-flop?”

Resposta: Dois estados estáveis (0 e 1)

Categoria 7: Tabelas Verdade

Questão: “Na tabela verdade do RS, o que significa Qprev?”

Resposta: Estado anterior é mantido (sem alteração)

Questão: “No flip-flop JK, o que acontece quando J = 0 e K = 0?”

Resposta: Mantém estado anterior (memória)

Questão: “Como identificar operação de SET na tabela verdade?”

Resposta: Saída Q = 1 (RS: S=1,R=0; JK: J=1,K=0; D: D=1)

Categoria 8: Aplicações Práticas

Questão: “Para que serve um flip-flop em modo toggle?”

Resposta: Contadores binários e divisores de frequência

Questão: “Qual flip-flop é ideal para armazenamento de dados?”

Resposta: Flip-flop D (determinístico, entrada única)

Questão: “Como construir um contador binário?”

Resposta: Conectando flip-flops T ou JK em cascata

DICAS PARA RESOLUÇÃO DE QUESTÕES ANAC

- Memorize as implementações: RS = 2 NAND, JK = 4 NAND

- Lembre-se da sincronização: Mudanças só na borda de subida

- Identifique o tipo: Cada flip-flop tem características únicas

- Analise as entradas: Correlacione com a tabela verdade correspondente

- Considere aplicações: Toggle para contadores, D para dados

- Atenção aos estados: RS tem inválido, JK não tem

- Divisão de frequência: T sempre divide por 2

- Terminologia: “Sistemas pulsados”, “borda de subida”, “toggle”

FAQ

P: Qual é a diferença prática entre circuitos combinacionais e sequenciais?

R: Nos combinacionais a saída depende somente das entradas presentes; nos sequenciais a saída também depende do estado armazenado, graças aos flip-flops. Isso permite contadores, registradores e controle de estados.

P: Por que a banca enfatiza “borda de subida”?

R: Porque os flip-flops padrão do estudo mudam apenas nesse instante, o que evita alterações fora de hora e facilita o projeto síncrono e a análise temporal.

P: O que significa Qprev nas tabelas-verdade?

R: É o valor anteriormente armazenado. Quando a tabela indica “mantém (Qprev)”, a saída não muda naquela borda do clock.

P: Por que o FF-RS tem condição inválida e o FF-JK não?

R: No RS, S = 1 e R = 1 violam a complementaridade entre Q e Q̅, gerando indeterminação. O JK modifica a estrutura e transforma o caso “1 e 1” em comutação (toggle), eliminando a invalidação.

P: Em que situação devo preferir um FF-D?

R: Quando você precisa armazenar dados de forma determinística: na borda ativa, Q recebe exatamente o valor de D. É a base de registradores e sincronizadores de sinais.

P: Como reconhecer SET e RESET na prática?

R: SET força Q = 1 e RESET força Q = 0. Nas tabelas, procure as combinações que resultam nesses valores em Q na borda ativa do clock.

P: O que torna o FF-T um bom divisor de frequência?

R: Com T = 1, ele inverte a cada borda de subida, produzindo uma saída com metade da frequência do clock e duty cycle de 50%.

P: Quantas portas NAND são usadas nos FFs clássicos RS e JK?

R: O RS clássico usa duas NAND; o JK clássico usa quatro NAND, necessárias para implementar o modo toggle com realimentações adequadas.

P: O que acontece se eu violar setup ou hold time?

R: O flip-flop pode entrar em metaestabilidade, mantendo uma saída indefinida por um tempo e comprometendo todo o sistema. Por isso, temporização é tópico-chave.

P: “Latch” e “flip-flop” são a mesma coisa?

R: Ambos armazenam um bit, mas o latch é sensível ao nível (responde enquanto o controle está ativo) e o flip-flop é sensível à borda (responde apenas na transição).

P: Como derivar um FF-D a partir de um FF-JK?

R: Conecte D diretamente a J e, invertido, a K. Assim, D = 1 implica J = 1 e K = 0 (SET); D = 0 implica J = 0 e K = 1 (RESET).

P: E o FF-T, dá para implementar com JK ou D?

R: Sim. Com JK: ligue J = K = T (T = 1 → toggle). Com D: alimente D = Q̅ quando T = 1 e D = Q quando T = 0 (por lógica simples), resultando no mesmo efeito.

P: Por que sistemas síncronos são preferidos em provas e projetos?

R: Porque o clock impõe ordem temporal, reduzindo condições de corrida e facilitando a verificação do comportamento em momentos bem definidos.

P: Como ler rapidamente uma tabela-verdade de flip-flop?

R: Identifique a coluna do clock (↑), veja as combinações de entrada e observe se o resultado é “mantém”, SET, RESET ou TOGGLE, lembrando que Q̅ é sempre complementar.

P: Contadores com FF-T seguem qual padrão de divisão?

R: Cada estágio divide por 2. Em cascata, n estágios dividem por 2ⁿ e contam de 0 até (2ⁿ − 1) em binário.